Physical Design

Be that Physical Designer with the world-class industry-oriented VLSI – Physical Design training program using the Cadence Encounter tool.

2000+ Engineers trainers provided to Industry!

Course Details

You need to qualify the screening test and technical interview. The test would be conducted in Basic Electronics – BJT, FET, CMOS; Digital Electronics – Number Systems, Boolean Algebra, K-Maps, Logic Gates, Logic Families, Combinational Circuits, Sequential Circuits, Counters, and aptitude. (All are subjective type questions)

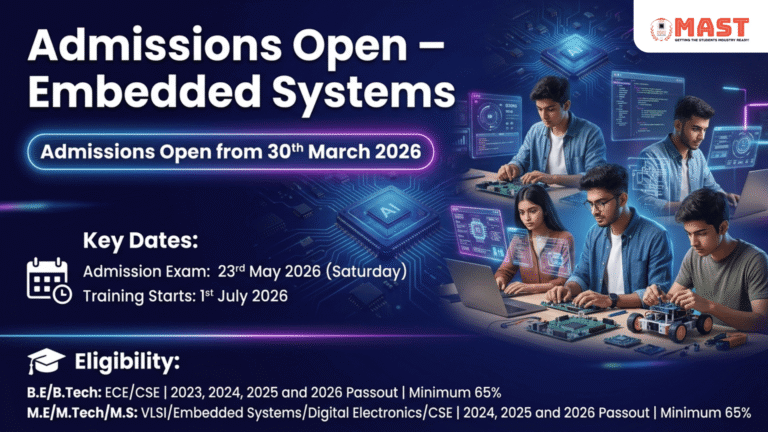

B.Tech – ECE/EEE | 2022, 2023, 2024, 2025 Passout | Minimum 65%

M.Tech – ECE/EEE | 2023, 2024 and 2025 passout | Minimum 65%

₹1,50,000/- [+ 18% GST].

Srinivasa Kakumanu (KS)

- 6 Months of practical learning

- Hands-on experience with Tools

- Placement Assistance

- Certificate of Completion

Course Content

RC Circuits: Lumped matter discipline, distributed matter discipline, delay of wire, Energy, power, average power, peak power, RC delays.

Digital Abstraction: Digital communication, forbidden region and noise margin in digital representation, Logic 0 noise margin and Logic 1 noise margin, representation of VOH, VIH, VIL, VOL, Static Discipline.

MOSFET: S Model, SR Model, MOSFET Characteristics, Power consumption in logic gates, CMOS logic

CMOS process: Fabrication, Design of CMOS schematics and Stick Diagrams, standard cell

Digital Circuit Speed: Different drive strengths, timing Arcs, switching rate vs propagation delay of gate, wire delay vs buffer insertion.

Combinational Circuits I and II: Potential problems in netlist, all combinational circuits- Mux, Comparator, Decoder and Encoder, Transmission Gates and Pass Transistor Logic, tristate gates, Adders, CMOS implementation of adders, sizing of CMOS adders.

Sequential Circuits I and II: Latch, Flop, timing arcs and constraints, setup and hold requirements, Slacks, problems on setup and hold slacks with skew and jitter, global skew and local skew.

TCL Scripting Assignments

Design problems, when circuits get asynchronous & Chip reset: Design problems on timing diagrams, Frequency divider, duty cycle, when events are synchronous, metastability, 2-stage synchronizer, MTBF, recovery, and removal times

Fundamentals of STA I: Inputs of STA, types of timing paths, SDF, LEC, SDC constraints, timing exceptions.

Logic Synthesis: Synthesis Flow and inputs, Wireload models, interpolation, extrapolation, low power synthesis techniques- ICG, multi-Vt, DRVs, synthesis strategy- flat, hierarchical synthesis, registering in – registering out, buffering in – buffering out, genus local attributes, optimization techniques, synthesis scan, physical synthesis, incremental synthesis, netlist uniquification, synthesis test cases.

Physical Design: Inputs for PNR, PNR Terminology, Partitioning, floorplan guidelines – blockages, Power planning- Power requirement for chip, chip top level (IOPADS, POWER PADS) and block level power distribution mechanism, level shifters, placement- timing driven placement, congestion fixing techniques, CTS, macro model, skew groups, routing, OCV, Parasitic extraction corners, Crosstalk analysis.

Fundamentals of STA II and miscellaneous concepts: Half cycle paths, multi-cycle paths, clock domain crossing, min-max delays, STA test cases, metal density rules, Antenna effects, Spare cells, ESD, TIE HI, TIE LOW cells, well taps, filler cells, latch up, bond pads, FINFET.

Start Getting New Knowledge and Experience, Together!

Get the job-oriented training from the Industry Experts & be Future-Ready!